This article summarizes how to install and integrate the commercial SRAM from fabless Marketplace to your user project.

This tutorial demonstrates how to seamlessly integrate SRAM into your design using Caravel as the platform. While Caravan and openFrame are also viable options, we will focus on Caravel for this example. Our approach involves streamlining the controller and linking it to the SRAM within a macro for efficient integration.

Note that in this example, the Wishbone controller is used and included in the SRAM IP. However, you are free to use any bus wrapper of your choice.

Step 1:

Install IPM:

pip install ipmgr

Test IPM installation:

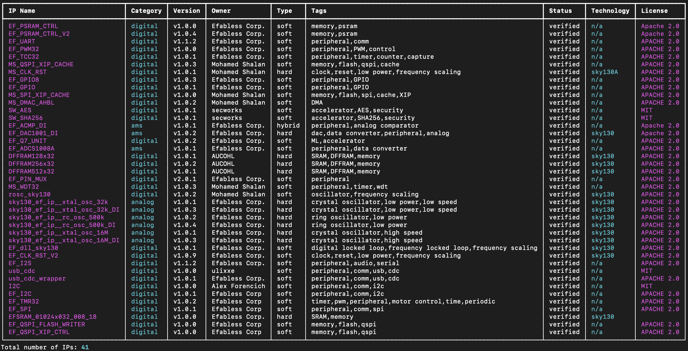

ipm ls-remote

You should see something like this:

For the purpose of this tutorial, we are interested in the EF_SRAM_1024x32 IP.

Step 2:

Create your project repository from our template:

Follow these steps from caravel user project repo

Setup your environment:

Start by cloning the repo you created:

git clone <repo url>

Setup the environment:

cd <repo name>

make setup

Install the SRAM IP:

Use this command to install the SRAM IP using IPM that we installed earlier in the tutorial

ipm install EF_SRAM_1024x32

This will download the IP inside your project directory, it will be found under ip/ directory. The directory structure of the IP is predefined as shown:

.

├── EF_SRAM_1024X32.yaml - Configuration file for IP

├── README.md - General information (or datasheet) for project

├── doc/ - Documentation files for the project

├── gds/ - GDSII files for the IP

├── hdl/ - Hardware Description language files

├── bus_wrapper/ - Bus wrapper hdl files

│ └── beh_models/ - Behavioral models

├── lef/ - Library Exchange Format files

├── lib/ - Liberty files for timing

└── mag/ - magic layout files

The SRAM datasheet can be found here.

Step 3:

To integrate the SRAM macro into the user project's Verilog, in order to interface the wishbone bus, the SRAM IP comes with a controller located in ip/EF_SRAM_1024x32/hdl/controllers/ram_wb_controller.v. This controller is not pre-hardened, so we will combine it with the SRAM IP inside a macro. The integration of the SRAM IP and controller can be found in ip/EF_SRAM_1024x32/hdl/bus_wrapper/SRAM_1024x32_wb_wrapper.v. This Verilog file will be used to harden our SRAM + controller macro.

Update user_proj_example openLane configuration file:

We'll create a new directory and copy everything inside the user_proj_example to it

mkdir openlane/SRAM_1024x32_wb_wrapper

Let's change openLane configuration file config.json:

- Create the file

openlane/SRAM_1024x32_wb_wrapper/config.jsonfile and copy the following configurations from this file.

For more information about the openLane configurations used, visit openLane's documentation. - Adjust the pin order by creating the file

openlane/SRAM_1024x32_wb_wrapper/pin_order.cfg. Ensure that all pins are oriented towards the south to facilitate smooth connection with the wishbone bus:

#BUS_SORT

#S

$40

wb_.*

wbs_.* - Create a

openlane/SRAM_1024x32_wb_wrapper/macro.cfgfile and add the macro placement:SRAM_0 10.1 40 W

- Create a

openlane/SRAM_1024x32_wb_wrapper/pdn.tclfile, this will edit the PDN to add metal 4 stripes to make the integration to the top level easier. The PDN script can be found here. - Create a

openlane/SRAM_1024x32_wb_wrapper/base.sdcfile, this will define the timing constraints of the SRAM wishbone wrapper. The SDC file can be found here.

Harden the SRAM + controller macro:

Now we need to run the openLane flow to harden the macro we created above, this can be done with one command from the root directory of your project:

make SRAM_1024x32_wb_wrapper

The flow should start running, and after a couple of seconds you should see something like this:

NOTE: The klayout DRC error is a known issue with the DRC deck, if by the time you are trying this tutorial, it didn't spit out a DRC error, it is because we fixed it.

Step 4:

To integrate the SRAM macro with the user_project_wrapper, we have to start by editing the rtl/user_project_wrapper.v, to add the SRAM macro:

SRAM_1024x32_wb_wrapper mprj (

`ifdef USE_POWER_PINS

.VPWR(vccd1), // User area 1 1.8V power

.VGND(vssd1), // User area 1 digital ground

`endif

.wb_clk_i(wb_clk_i),

.wb_rst_i(wb_rst_i),

// MGMT SoC Wishbone Slave

.wbs_cyc_i(wbs_cyc_i),

.wbs_stb_i(wbs_stb_i),

.wbs_we_i(wbs_we_i),

.wbs_sel_i(wbs_sel_i),

.wbs_adr_i(wbs_adr_i),

.wbs_dat_i(wbs_dat_i),

.wbs_ack_o(wbs_ack_o),

.wbs_dat_o(wbs_dat_o)

);

endmodule // user_project_wrapper

This should be added after:

/*--------------------------------------*/

/* User project is instantiated here */

/*--------------------------------------*/

Update the user_project_wrapper openLane configuration file:

- Add the generated files that we generated in the step before, these include verilog, GDS, LEF, lib and SPEF files:

"VERILOG_FILES_BLACKBOX": [

"dir::../../verilog/gl/SRAM_1024x32_wb_wrapper.v"

],

"EXTRA_LEFS": "dir::../../lef/SRAM_1024x32_wb_wrapper.lef",

"EXTRA_GDS_FILES": "dir::../../gds/SRAM_1024x32_wb_wrapper.gds",

"EXTRA_LIBS": "dir::../../lib/SRAM_1024x32_wb_wrapper.lib",

"EXTRA_SPEFS": [

"SRAM_1024x32_wb_wrapper",

"dir::../../spef/multicorner/SRAM_1024x32_wb_wrapper.min.spef",

"dir::../../spef/multicorner/SRAM_1024x32_wb_wrapper.nom.spef",

"dir::../../spef/multicorner/SRAM_1024x32_wb_wrapper.max.spef"

], - Update the macro PDN hooks:

"FP_PDN_MACRO_HOOKS": "mprj vccd1 vssd1 VPWR VGND"

- Turnoff the magic DRC check as the macro is abstract and magic doesn't know how to run DRC on an abstract macro:

"QUIT_ON_MAGIC_DRC": false,

- Adjust the macro placement using the

openlane/user_project_wrapper/macro.cfgfile:mprj 15.06 115 N

Harden the user_project_wrapper:

from the project root run the flow to harden the user_project_wrapper

make user_project_wrapper

Now you should get a fully integrated SRAM IP macro inside the user_project_wrapper. You can view the final GDS from gds/user_project_wrapper.gds, using any tool of your liking, example: Klayout.

This is how the fully integrated wrapper should look like

Resources:

- The example in this tutorial can be found in this repo

- Efabless webinar going through the whole process YouTube video

- Efabless Marketplace